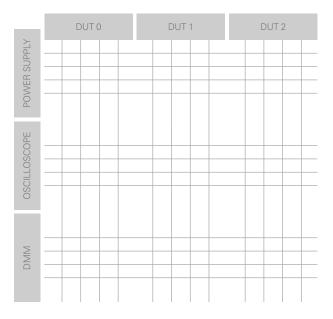

# Fundamentals of Building a Test System

02

Modeling the Total Cost of Ownership of an Automated Test System

12

**Selecting Instrumentation**

26

Automated Test System Power Infrastructure

42

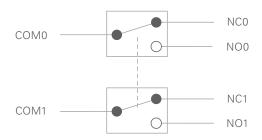

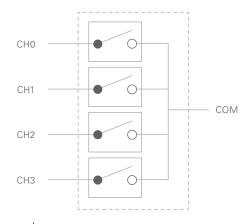

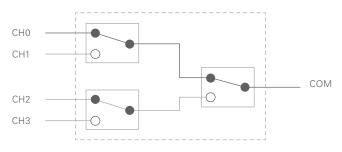

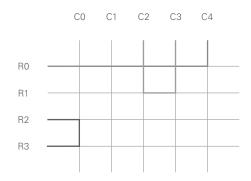

Switching and Multiplexing

66

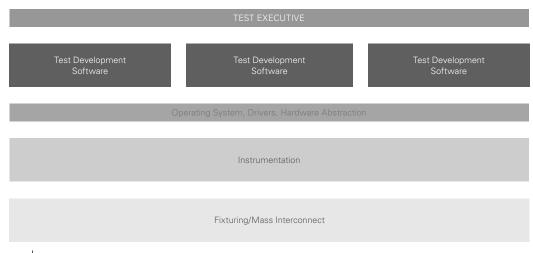

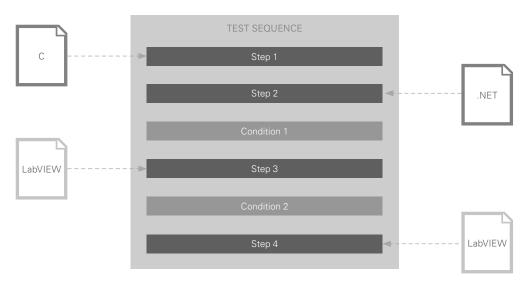

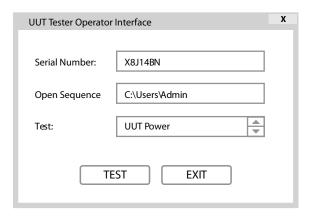

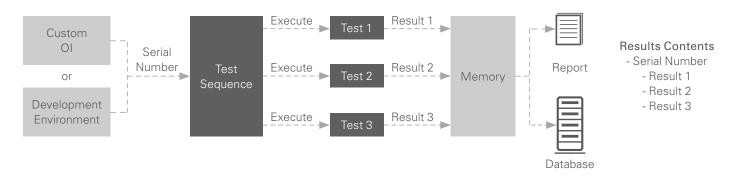

**Test Executive Software**

78

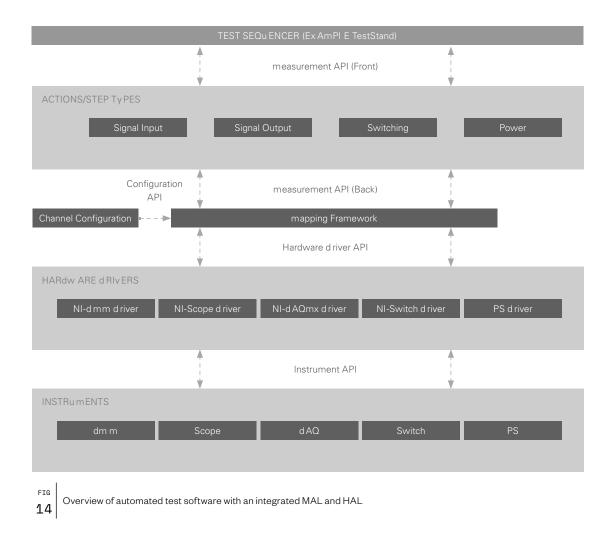

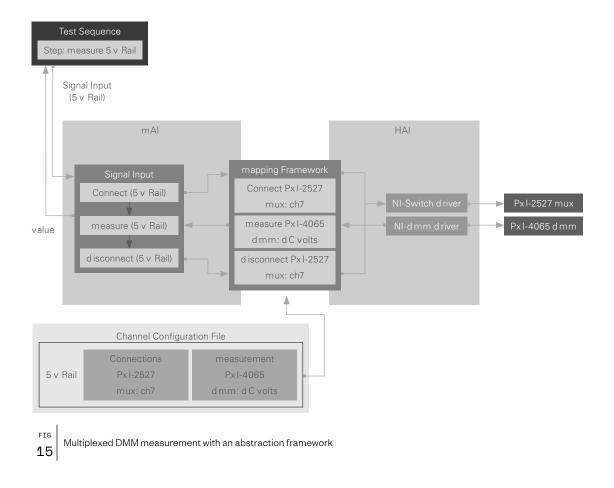

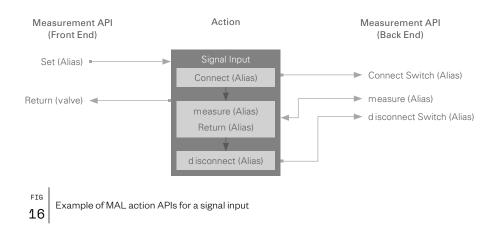

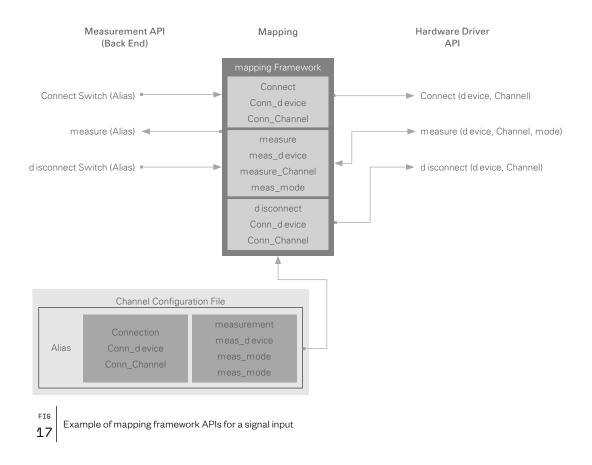

Hardware and Measurement Abstraction Layers

107

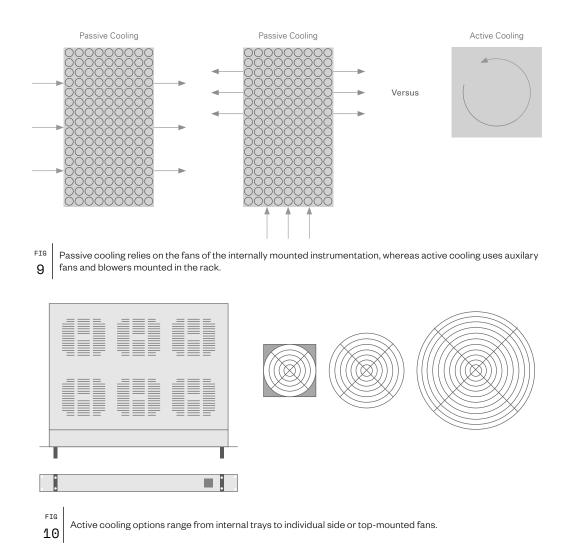

Rack Layout and Thermal Profiling

122

Mass Interconnect and Fixturing

133

Software Deployment

151

System Maintenance

# Modeling the Total Cost of Ownership of an Automated Test System

03 INTRODUCTION

04 DEVELOPMENT COSTS

05 DEPLOYMENT COSTS

06 OPERATION AND MAINTENANCE COSTS

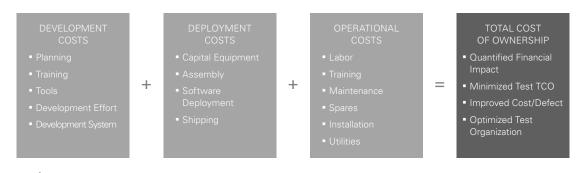

FINANCIAL ANALYSIS APPROACHES

07 PRACTICAL SCENARIO

11 conclusion

## Introduction

Most organizations do not consider production test a top priority, but it is a necessity to prevent major quality issues in the products that represent the company brand in the hands of customers. The costs, however, can be significant and are often greatly misunderstood, especially when there's no easy way to quantify the positive business impact of high-quality products or shortened time to market. But best-in-class organizations are unfazed by this "necessary evil" viewpoint, because they seek to understand the total cost of developing, deploying, and maintaining test systems to get ahead of this perception. And the cost of automated test, in reality, is far more complex than the capital cost of a test rack or even the operator's hourly rate.

In this guide, learn about the tools and insight you need to evaluate your test organization, propose changes where significant cost savings are available, and improve the profitability of your company year over year with smarter investment decisions.

Proper modeling of total cost of ownership uncovers all the lifetime costs of certain test assets and provides a financial framework for justifying future strategic investments.

# **Development Costs**

For most applications, the development costs associated with building a customized automated test system are the smallest in relation to the deployment, as well as operation and maintenance costs. This is typically because only one system is built to serve as a proof of concept for performance benchmarking and test coverage assessment. However, the total cost for developing a test system can vary significantly, depending on the end goal. An organization that is creating a new product often develops and compares multiple test systems with different architectures and instrumentation to identify the optimal approach.

The R&D (engineering) team responsible for a product designs and builds the majority of development systems, and the costs, therefore, are rolled into this budget or cost center. More mature test departments work with their R&D teams to influence the design of products, often referred to as design for test, or DFT, and also work to develop the test systems. This is a best practice but not always possible for test organizations.

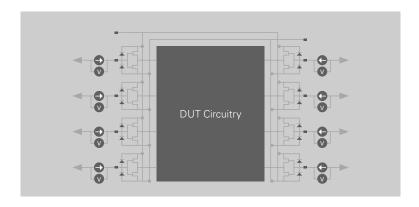

For test systems built to test the functionality of a single device or component, the level of effort involved with requirements gathering, instrumentation selection, fixturing, and software development are relatively finite. If, however, a test department is designing a multipurpose, standardized test system to verify the functionality of multiple devices or components, development costs can be greater. You must spend more time identifying all permutations of functionality that the system must accomplish, device under test (DUT) fixturing must be flexible, and the software must be more scalable to make it easy to implement changes when adding new devices to the product portfolio.

Other efforts, such as writing a hardware, measurement abstraction layer or mass interconnect system, require significantly more upfront development cost, but should pay a return on investment for test organizations that either deal with rapid technology change or face instrumentation end-of-life (EOL) issues for long life-cycle systems.

The main costs associated with developing an automated test system are:

- Planning Effort—Entails the time and expenses required to properly identify all viable options for the test system. It includes time spent at vendor websites, product demonstration sessions, evaluations, trade shows, and discussion forums.

- Developer Training—Includes the time and training course fees associated with learning a new set of software development tools (integrated development environment [IDE] or test executive) and hardware platforms (for example, rack and stack with SOSI or PXI).

- Development Tools—The cost associated with purchasing development licenses for the test software (IDE or test executive).

- **Development Effort**—The time associated with the hardware and software development of a proof-of-concept test system.

- Development System—The capital cost associated with purchasing the initial proof-of-concept or demonstrator test system for benchmarking against current or other new systems.

# **Deployment Costs**

When you put a product into production, you must scale up the proof-of-concept or demonstrator test system to meet the volume demands of the product. The throughput (units tested per amount of time) of the test system directly impacts the number of systems required to meet demand, and product management and the sales channel determine the forecasted volume. Alongside coverage of test functionality, the required number of test systems is the factor that you should consider most during the development phase because this directly impacts the total deployment cost.

Another factor that increases a test system's deployment cost is shipping. Smaller organizations find this less challenging because the manufacturing test and R&D departments can be collocated in the same building or at least in close geographic proximity. However, even some smaller companies opt to contract the manufacturing and test of their products if they lack the ability or expertize to manufacture and test their devices or components. Larger companies, however, can have manufacturing test and R&D departments located in separate regions within the same country, and even in a completely different country. This can increase deployment costs dramatically, especially if the manufacturing test system is large and/or heavy. Slower freight shipping methods can help to reduce this cost, but only in circumstances where time is not a factor. A best practice is to consider the physical size and weight of any test system during the development phase, especially when comparing two options, as this can bear a significant downstream cost.

Traditional, Box-Instrument Test System

PXI Test System

When selecting between two test systems with similar performance, select the smaller, lighter test system to reduce deployment costs.

The main costs associated with deploying an automated test system are:

- Capital Equipment—The number of test systems required, which is determined by the product demand and test system throughput, directly impacts this cost.

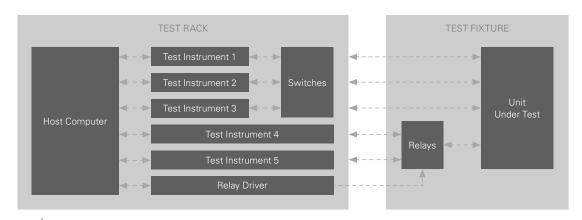

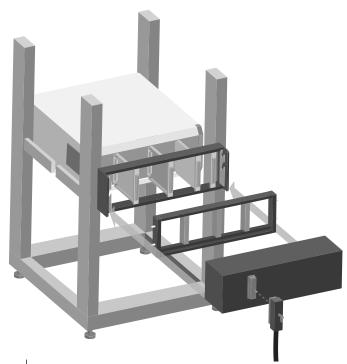

- System Assembly—The time required to assemble the individual components into a test system, which includes building a 19 in. or 21 in. instrumentation rack or other mechanical enclosure, installing all test instrumentation, connecting cabling and wiring, installing switching and mass interconnect, and fixturing.

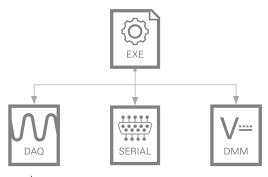

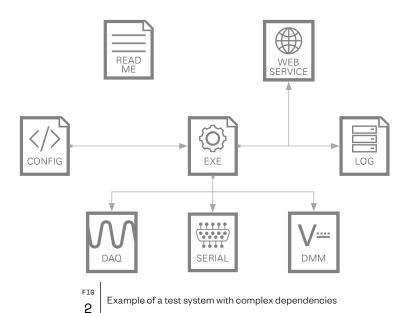

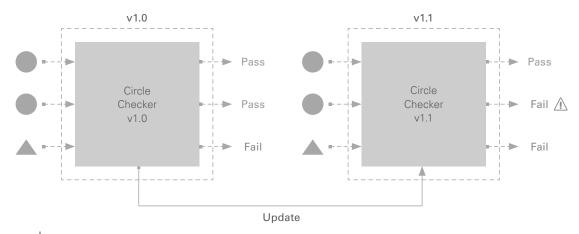

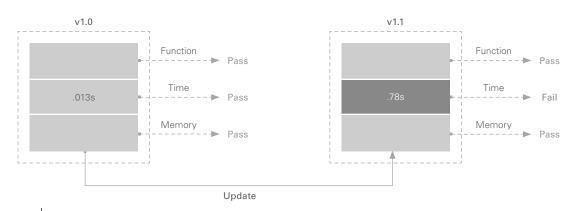

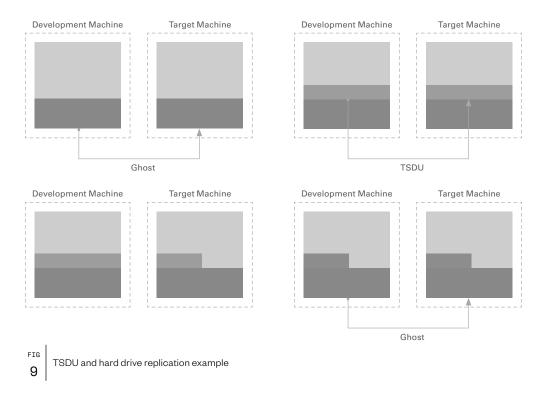

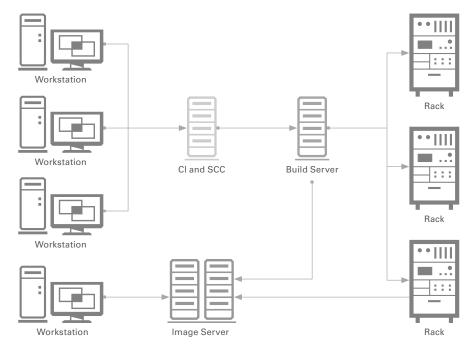

- Software Deployment—These costs are associated with compiling or building a collection of software components and then exporting these components from a development computer to target machines for execution.

- Shipping and Logistics—The size and weight of the test system as well as the quantity of test systems required for the production or manufacturing facility directly impact this cost. The distance travelled and the time window required to receive the shipment also impacts the cost. Depending on the ruggedness of the system, special packaging may be necessary.

# **Operation and Maintenance Costs**

The final and often overlooked or underappreciated costs associated with a test system are the operation and maintenance costs. These are typically not attributed to the R&D team that originally designed the product or device but almost always roll up to the manufacturing or production team; this separation of cost centers makes cross-department collaboration a common pain point. In situations where a company chooses to contract out the manufacturing and test of its products, the contract manufacturer incurs the individual costs and negotiates a flat or hourly rate for the service.

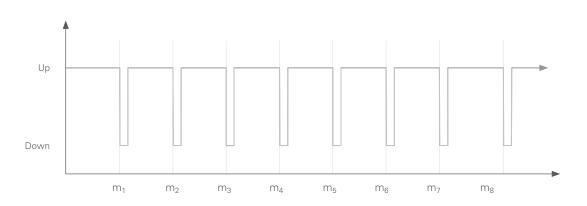

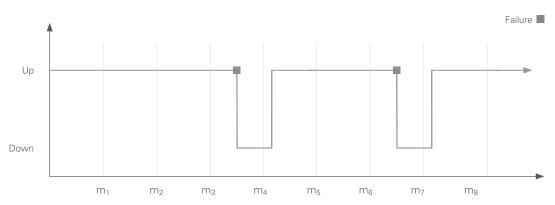

The costs associated with operating and maintaining an automated test system are:

- Hourly Operation—The labor costs for test system operators and support technicians to ensure the systems are up and running during manufacturing. The number of test systems and the skill level required to operate the system directly impact this amount.

- Operator Training—The time required for each operator to learn how to use a test system. Costs typically are limited to the amount of time that each operator must attend training, regardless of format (manual, online, or in-person). Companies with a variety of test systems must decide on their staffing strategy between a model of every operator can operate every test system and each operator specializes on a single test system.

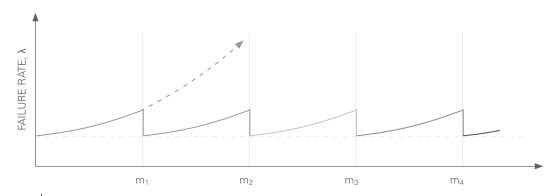

- Maintenance—The cost associated with keeping the test system and instrumentation in working order. It often includes the cost for annually calibrating equipment, as well as a forecasted cost for replacing instrumentation upon failure. How easy the system is to service can also impact this.

- Spare Inventory—The cost required to keep spare instrumentation in the event of unplanned downtime (for example, instrument failure) or planned downtime (for example, calibration). Each test system requires spare instrumentation; companies with multiple unique test systems, because of high product mix, require a larger set of spare instrumentation and parts for their test fleet to ensure high uptime.

- Installation—Test systems that consume a lot of power or produce a lot of heat need special, high-power electrical work or cooling towers to be installed to ensure proper performance.

- Utilities—The cost associated with powering, cooling, and housing (floor space) the test system. The price per square foot of the manufacturing floor and electricity rate can vary significantly based on geographic location.

# Financial Analysis Approaches

Because development and deployment costs are amortized over multiple years and operation and maintenance costs occur in the future, you must use a financial model to determine the total cost of ownership for a test system. For traditional investment scenarios, a project will generate revenue and profit. In this situation, however, there is no revenue or profit but rather a relative savings of one test system in comparison to another. Consider a similar situation that involves investing in high-efficiency lighting or building insulation, which costs money upfront—but money will be made through reduced utility expenses in the long run.

Payback Period (PP)—This is the amount of time it takes to recuperate the money you invest in a project. The calculation has two parts. First, you must determine the upfront costs by finding the difference in developing and deploying the new test system and deploying more of the old system. Because the old system has already been developed, there are no associated costs. Second, this difference is divided by the annual savings in operation from the new system's efficiency (throughput).

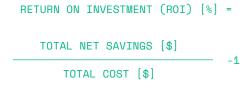

Return on Investment (ROI)—This is the ratio of the money earned to the money invested over the life of a project, expressed in a percentage. The calculation is more involved as it requires you to calculate the projected total cost of ownership for both the old and new options, and then find the difference in the two. You then divide this result by the total cost of the more cost-effective option, and subtract 1 (100%) from the quotient to find the resulting percentage.

• Additional Models—To determine the viability of projects or financial investments, you can use many additional financial models such as internal rate of return (IRR), net present value (NPV), and modified internal rate of return (MIRR). But most of the advanced modeling that comes with these drops out when comparing two options against one another, and you can simplify the analysis to PP and ROI.

## **Practical Scenario**

The following practical scenario helps demonstrate how you can use financial analysis of total cost of ownership to make an informed decision about purchasing a new test system architecture instead of keeping an old approach.

#### Overview

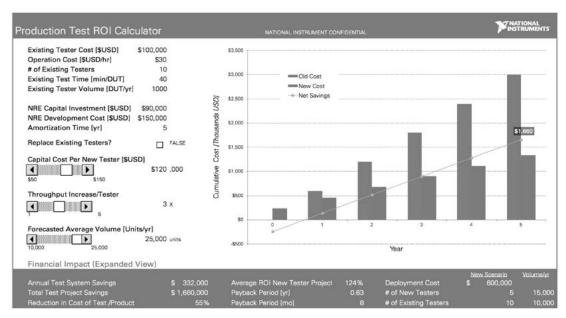

Company B is a \$200 million manufacturer of IP-based satellite communication systems. Their current production test system is architected using traditional rack-and-stack box instruments. Company B develops and deploys these test systems to a contract manufacturer who charges them a flat rate of \$30 per hour to perform product test.

The following best characterizes the current test system:

- Fully functional and full test coverage

- Moderate capital cost

- Organization is fully trained on how to operate

- Throughput is less than optimal

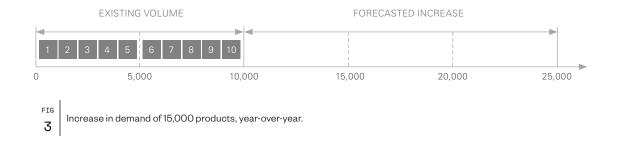

Because Company B recently invested in a larger sales channel and was able to enter new markets for their radar products, their production capacity must increase from 10,000 units to 25,000 units per year.

Their engineering team worked with NI to specify a new PXI-based test system that should result in a 3X improvement in test time per DUT. However, a new solution would require upfront development and deployment costs, so the business impact of the migration must be modeled relative to purchasing additional testers based on the previous architecture before a decision can be made.

### Development and Deployment Costs

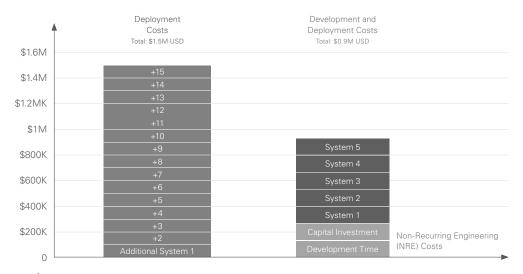

The most common assumption during this evaluation process is that it is more economical to buy additional test systems based on the existing architecture, because the organization is already fully trained and there are no incurred development costs. The system is already architected, and it just needs to be replicated. The new system, however, requires planning, architecting, training, and other nonrecurring engineering (NRE) costs during the development period.

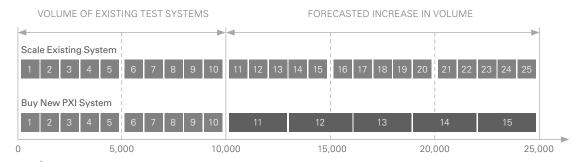

The throughput advantage of the new system, however, cannot be ignored; throughput directly determines the number of additional or new test systems that must be purchased to reach the forecasted increase in volume. In this scenario, scaling up the number of existing test systems requires 15 additional systems, whereas buying new PXI-based systems requires only five to meet the production volume.

| EXISTING RACK-AND-STACK SYSTEM |                        |

|--------------------------------|------------------------|

| NRE Capital Investment:        | N/A                    |

| NRE Development Time:          | N/A                    |

| Capital Expense:               | \$100,000 per system   |

| # Existing Test Systems:       | 10                     |

| Test Time:                     | 40 minutes per device  |

| Volume/Throughput:             | 1,000 devices per year |

| NEW PXI-BASED SYSTEM     |                        |

|--------------------------|------------------------|

| NRE Capital Investment:  | \$90,000               |

| NRE Development Time:    | \$150,000              |

| Capital Expense:         | \$120,000 per system   |

| # Existing Test Systems: | N/A                    |

| Test Time:               | 13 minutes per device  |

| Volume/Throughput:       | 3,000 devices per year |

| OTHER FINANCIAL VARIABLES |                              |

|---------------------------|------------------------------|

| Amortization Schedule:    | 5 years                      |

| Replace Existing Systems: | No, keep in operation        |

| Operation Cost per Hour:  | \$30 (contract manufacturer) |

| Required Throughput:      | 25,000 units per year        |

The 3X throughput improvement of the new PXI test system greatly reduces the number of systems required to meet additional product demand.

After determining the number of test systems required for each approach, you can compare the total cost associated with the development and deployment and directly understand the impact of throughput, capital expense, and NRE.

Even though the new PXI-based test system incurs NRE development costs, the total cost of development and deployment for the new system is \$600,000 less expensive.

For this given scenario, when comparing the development and deployment costs, buying a new solution is more cost-effective than scaling up the existing test system. The biggest driver of the inflated costs for scaling up the existing system is the low throughput of the system. Throughput alone increases the deployment costs by requiring three times as many test systems to meet the required volume.

But what happens if the variables change? Model different what-if scenarios to ensure that it is a profitable outcome, even in the worst-case scenario.

Some hypothetical scenarios to model:

- What if development time of the new system takes twice a long, and is therefore twice as expensive?

- What if the capital expense increases by 10 percent because of currency inflation?

- What if the throughput improvement is only 1.5X instead of 3X?

- What if the sales volume is revised from 25,000 to only 20,000 units?

- What if additional floor space is limited?

- What if additional power or cooling must be installed at the test facility?

- What if the previous instrumentation is now EOL?

## Operation and Maintenance Costs

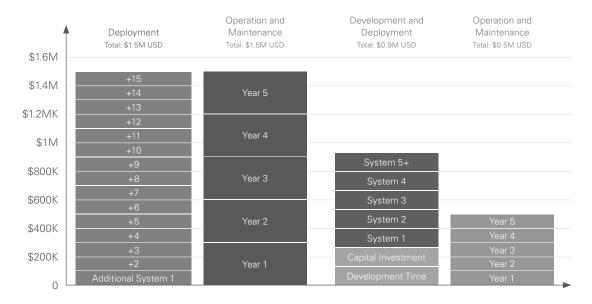

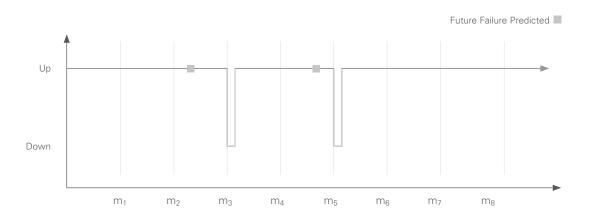

After you have developed and deployed the required number of test systems, you must operate and maintain them over the length of the project or product life cycle. The costs associated with operating and maintaining a test system are normally attributed to the company's manufacturing group, whereas the development and deployment of a test system are attributed to the R&D (engineering) group. Without guidance from leadership, the engineering team will likely default to cost optimize around development and deployment without considering the implications for the operation and maintenance costs.

In the example above where only development and deployment costs are considered, the new test system is more economical than purchasing additional test systems based on the previous architecture. Now analyze the operation and maintenance costs of the two options over the first five years of the project to understand the impact on the total cost of test.

In this situation, Company B has contracted the manufacturing and test of its products. The contract manufacturer charges Company B \$30 per hour to operate the test system.

In addition to having much lower development and deployment costs, the operation and maintenance costs of the PXI-based test system are much lower than the previous system's.

## Total Cost of Ownership

Although in this scenario the PXI option is the best choice, it is still important to determine the total cost of ownership to effectively model the financial benefit of the new system. This five-year analysis provides insight into variables such as PP, ROI, total savings, and reduction in cost of test on a per part basis. For this analysis, the development and deployment costs are amortized equally (flat) over a five-year period.

The new test system generates a total savings of \$1.66 million in five years with a payback period of 11 months in comparison to scaling up the existing solution.

## Scenario Summary

In the case of deciding between these two options for a test system, there are many factors to consider. The common assumption is that scaling up the old solution is easier and cheaper, but further analysis reveals that investing in a newer, higher performance system is a superior financial decision. The biggest factor in the financial advantage of the PXI system is

the 3X improvement in throughput—this allowed Company B to purchase one-third as many test systems to accomplish the same task, which saves them money on the capital investment. Over the five-year period, this also reduces the operation and maintenance costs that they pay to the contract manufacturer significantly, resulting in a PP of 11 months and a 124 percent ROI on the project.

## Conclusion

As device complexity and time-to-market pressures continue to soar, the total cost of ownership for an automated test system will continue to play an important role in a company's profitability. To realize this goal, you must look beyond the initial capital cost of the test system to ensure that all relevant costs are factored into your purchasing decisions. This guide focuses on automated production test, but you can extrapolate and apply the same concept to other phases of bringing a product from initial concept to the end user, including R&D, characterization, verification, and validation.

As the developers of the PXI platform, LabVIEW graphical system design software, and TestStand test management software as well as a founding member of the PXI Systems Alliance, NI has 40 years of experience helping companies to develop automated test systems for industries ranging from semiconductor production to aerospace and defense. Our direct field engineer team in more than 50 countries worldwide is committed to helping companies, large and small, ensure the highest product quality while reducing the cost of test. To take the next step, contact your local NI representative.

# Selecting Instrumentation

- 13 INTRODUCTION

- 14 ANALOG AND RF INSTRUMENTATION

- 18 DIGITAL INSTRUMENTATION

- 21 FORM FACTOR

- 25 NEXT STEPS

## Introduction

Engineers can generally agree on the high importance of the adage "pick the right tool for the job." Using the wrong tool can waste time and compromise quality, whereas the right tool can deliver the correct result in a fraction of the time.

When building automated test systems, the primary tools at your disposal come in the form of measurement instruments. These instruments include known commodities like digital mulitmeters (DMMs), oscilloscopes, and waveform generators as well as a variety of new and changing categories of products like vector signal transceivers and all-in-one oscilloscopes.

To select instrumentation, a skilled test engineer must be knowledgeable and proficient in navigating:

- Technical measurement requirements of the device under test (DUT)

- Key instrument specifications that will influence an application

- Various categories of instrumentation available and the trade-offs in capabilities, size, price, and so on

- Nuanced differences between product models within a given instrument category

Picking the right tool for the job is much easier said than done, specifically when it comes to navigating and evaluating the many trade-offs at play. In this guide, see the major categories of instruments available, and learn about common selection criteria to help you narrow in on the best choice for your application.

# Analog and RF Instrumentation

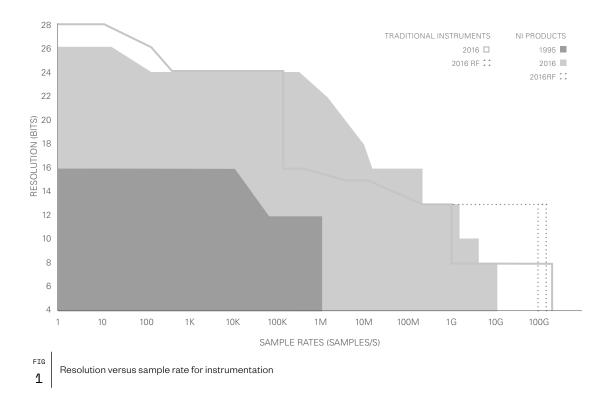

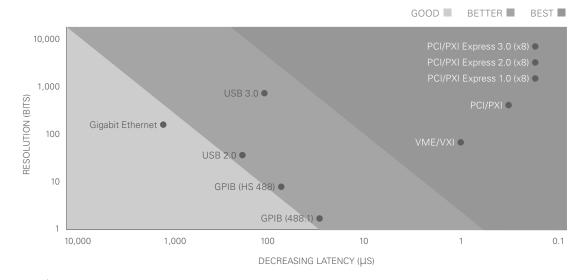

The landscape of analog and RF test instruments is very broad, with thousands of models across hundreds of product categories. At the same time, it is also predictably governed by the laws of physics—specifically, the fundamentals of noise and bandwidth manifest in the form of amplifier technology and analog-to-digital converters (ADCs) that are used to create instruments. These fundamental physics limitations create a very discernable trade-off in the precision of a measurement compared to the speed at which it can be acquired. Shown below is a view of how that speed versus resolution trade-off has evolved over time as technology has progressed in both traditional and modular instruments.

## Analog and RF Instrument Categories

The curve in Figure 1 represents examples from a variety of different instrument categories. DMMs provide high accuracy at low speeds at the top left of the chart, oscilloscopes provide high-frequency acquisitions at lower resolutions on the bottom right of the chart, and DAQ products offer higher channel densities and lower cost in the bottom left.

To narrow in on which category of instrument to begin looking into, first consider a couple of key questions about your measurement task:

- What is the direction of the signal? (input, output, or both)

- What is the frequency of the signal? (DC, kilohertz, megahertz, or gigahertz)

Given the answers to those two key questions on directionality and speed, there's generally a natural starting point for the instrument category you should consider, which Table 1 can best describe.

#### Analog Instrumentation Categories

|                                        | DC AND POWER                 | LOW-SPEED ANALOG                                         | HIGH-SPEED ANALOG                                       | RF AND WIRELESS                                                               |

|----------------------------------------|------------------------------|----------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------|

| INPUT, MEASURE                         | Digital Multimeter           | Analog Input, Data<br>Acquisition (DAQ)                  | Oscilloscope,<br>Frequency Counter                      | RF Analyzer<br>Power Meter<br>(Spectrum Analyzer,<br>Vector Signal, Analyzer) |

| OUTPUT, GENERATE                       | Programmable Power<br>Supply | Analog Output                                            | Function/Arbitrary<br>Waveform Generator<br>(FGEN, AWG) | RF Signal Generator<br>(Vector Signal<br>Generator, CW Source)                |

| INPUT AND OUTPUT ON<br>THE SAME DEVICE | DC Power Analyzer            | Multifunction Data<br>Acquisition<br>(Multifunction DAQ) | All-in-One<br>Oscilloscope                              | Vector Signal<br>Transceiver (VST)                                            |

| INPUT AND OUTPUT ON<br>THE SAME PIN    | Source Measure Unit<br>(SMU) | LCR Meter                                                | Impedance Analyzer                                      | Vector Network<br>Analyzer (VNA)                                              |

This chart, although helpful, is far from an exhaustive list of instrument types, especially regarding vertical or specific-purpose instruments.

Some noteworthy areas that the table does not cover include:

- Specialty DC instruments such as electrometers, microohmmeters, nanovoltmeters, and so on

- Audio band analysis and generation (also known as dynamic signal analyzers)

- Specialty analog products including pulse generators, pulser/ receivers, and more

## Key Specifications to Consider

After you have narrowed a measurement task to a specific instrument category, the next step is to weigh the trade-offs among products within that category regarding requirements including:

- Signal ranges, isolation, and impedance—First, make sure an instrument's input signal range is large enough to capture the signals of interest. Additionally, consider an instrument's input impedance, which affects the loading and frequency performance of the measurement setup, and an instrument's isolation from ground, which impacts noise immunity and safety.

- Analog bandwidth and sample rate—Next, make sure that the instrument can pass through the signals of interest based on their analog bandwidth (represented in kilohertz, megahertz, or gigahertz) and that the ADC can sample fast enough to capture the signal of interest (represented in samples per second such as kilosamples per second, million samples per second, or gigasamples per second).

- Measurement resolution and accuracy—Finally, evaluate multiple aspects in an instrument's vertical specifications that influence the quality of the measurement such as ADC resolution (digital quantization of analog signals, generally between 8-bit up to 24-bit), measurement accuracy (maximum measurement error over time and temperature, generally expressed in percent or parts per million), and measurement sensitivity (the smallest detectable change, generally expressed in absolute units such as microvolts)

Instruments that don't comprise in these functional dimensions of range, accuracy, and speed will likely present other tradeoffs in terms of price, size, power consumption, and channel density—all of which influence an instrument's utility.

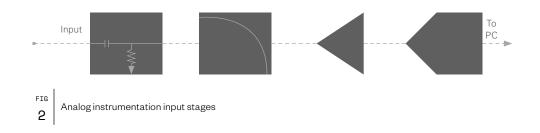

Figure 2 shows a simplified view of the analog input path of a generic measurement instrument with four key input stages, the instrument specs those stages influence, and the example instrument specifications of a typical DMM and a typical oscilloscope as influenced by that stage.

The below simplification can be a helpful construct to sift through instrument specifications, which are often presented using a variety of different nomenclatures across instrument categories and across instrument vendors. These stages are often interdependent in influencing key specifications. For instance, the input amplifier can also influence the input bandwidth and the effective resolution of an instrument. Similarly, the input impedance of an instrument can have major effects on the bandwidth.

### Analog Instrumentation Input Stages

|                             | INPUT ISOLATION AND TERMINATION                       | INPUT COUPLING<br>AND FILTERING                       | INPUT AMPLIFIER                              | ANALOG-TO-DIGITAL<br>CONVERTER (ADC)                      |

|-----------------------------|-------------------------------------------------------|-------------------------------------------------------|----------------------------------------------|-----------------------------------------------------------|

| SPECIFICATION<br>DETERMINED | Isolation Input<br>Impedence                          | AC/DC Coupling<br>Analog Bandwidth                    | Max Voltage Range<br>Min Voltage Sensitivity | Sample Rate<br>Resolution                                 |

| EXAMPLE DMM:                | Isolalted up to 330 V<br>Cat II 10 MΩ<br>(Selectable) | DC coupled 200 kHz<br>bandwidth                       | Up to 300 V input down to 10 nV sensitivity  | 10k Hz reading rate<br>6.5-digital (24-bit)<br>resolution |

| EXAMPLE:<br>OSCILLOSCOPE:   | Ground referenced 50 Ω or 1 MΩ (Selectable)           | DC or AC coupled<br>(Selectable)<br>350 MHz bandwidth | Up to 40 Vpp input down to 1 mV sensitivity  | Up to 5 GS/s sample rate 8-bit resolution                 |

## Analog and RF Instrument Categories

As you compare the measurement requirements of your DUT and the capabilities of the instruments you'll use to test them, keep in mind the following critical ratios.

#### Test Accuracy Ratio = 4:1

When testing a component, such as a voltage reference, make sure that the accuracy of your measurement equipment is substantially larger than the accuracy of the component being measured. If this criterion is not satisfied, measurement error can be significantly caused by both the DUT and the test equipment, making it impossible to know the true source of error. Because of this, the concept of test accuracy ratio (TAR) is employed to illustrate the relative accuracy of the measurement equipment and the component under test.

Acceptable values for TAR are four and above, depending on the test being performed and the test certainty that is required.

TAR = WANTED ACCURACY OF THE COMPONENT UNDER TEST

ACCURACY OF MEASUREMENT EQUIPMENT

#### Bandwidth Ratio = 5:1

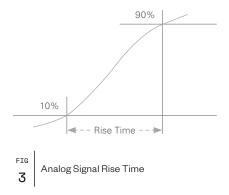

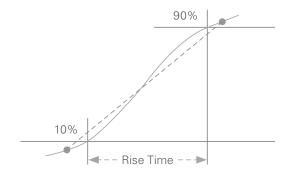

Rise time and bandwidth are directly related, and one can be calculated from the other. Rise time defines the time a signal takes to go from 10 to 90 percent of its full-scale value.

As a guideline, use the following equation to figure out the bandwidth of your signal based on its rise time:

Ideally, you should use a digitizer with three to five times the bandwidth of your signal as calculated in the equation above. In other words, your digitizer's rise time should be 1/5 to 1/3 of your signal's rise time to acquire your signal with minimal error.

You can always backtrack to determine your signal's real bandwidth based on the following formula:

$$T_{\text{m}} = \sqrt{T_{5}^2 + T_{d}^2}$$

Tm = MEASURED RISE TIME,

T<sub>5</sub> = ACTUAL SIGNAL RISE TIME,

$T_d = DIGITIZER'S RISE TIME$

#### Time Domain Sampling Ratio = 10:1

Whereas bandwidth describes the highest frequency sine wave that can be digitized with minimal attenuation, sample rate is simply the rate at which the ADC in the digitizer or oscilloscope is clocked to digitize the incoming signal. Sample rate and bandwidth are not directly related; however, there is a general rule for the wanted relationship between these two important specifications:

#### DIGITIZER'S REAL-TIME SAMPLE RATE =

#### 10 TIMES INPUT SIGNAL BANDWIDTH

Nyquist theorem states that to avoid aliasing, the sample rate of a digitizer needs to be at least twice as fast as the highest frequency component in the signal being measured. However, sampling at just twice the highest frequency component is not enough to accurately reproduce time-domain signals. To accurately digitize the incoming signal, the digitizer's real-time sample rate should be at least three to four times the digitizer's bandwidth. To understand why, look at the figure below and think about which digitized signal you would rather see on your oscilloscope.

Although the actual signal passed through the front-end analog circuitry is the same in both cases, the image on the left is undersampled, which distorts the digitized signal. On the contrary, the image on the right has enough sample points to accurately reconstruct the signal, which results in a more accurate measurement. Because a clean representation of the signal is important for time domain applications such as rise time, overshoot, or other pulse measurements, a digitizer with a higher sample benefits these applications.

The image above shows a digitizer with a sufficiently high sample rate to accurately reconstruct the signal, which will result in more accurate measurements.

# **Digital Instrumentation**

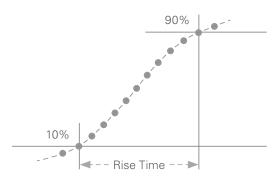

In the context of electronic functional test, digital instrumentation serves the purpose of interfacing with digital protocols and testing the electrical characteristics and communication link characteristics of those protocols. One of most critical aspects influencing the available instrumentation for a given task is parallel versus serial digital communications.

#### Parallel Versus Serial Standards

Serial standards have been gaining in popularity because of the physical limitation on the clock rates of parallel buses at around 1 GHz to 2 GHz. This is because of skew introduced by individual clock and data lines that cause bit errors at faster rates. Highspeed serial buses send encoded data that contains both data

and clocking information in a single differential signal, allowing you to avoid speed limitations in parallel buses. Serializing the data and sending at faster speeds allows pin counts of integrated circuits (ICs) to be reduced, which helps decrease size. Furthermore, because the serial lanes can operate at a much faster clock speed, they can also achieve better data throughput than what was possible with parallel buses.

#### **BUS STANDARDS**

CLOCK FREQ (Hz) or LINE RATE (bps)

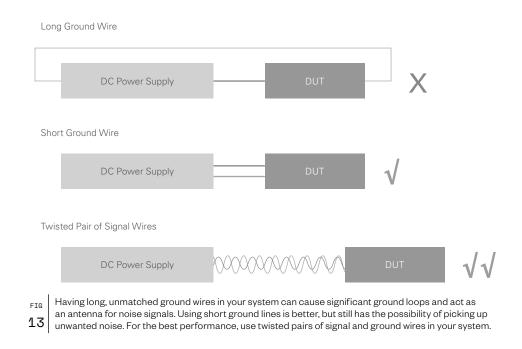

#### Parallel Bus Serial Bus 1 PCle Gen1x16 1 PCI 64-bit/33 MHz Ultra-2 wide SCSI 15 HDMI 1.3 16 HDMI 2.0 2 PCI 64-bit/66 MHz RapidIO Gen1.1 PCle Gen2x16 3 PCI 64-bit/100 MHz **GPIB** Serial RapidIO Gen2 3D-SDI 4 Front Panel Data Port SCSI 4 PCIe Gen3x16 Gigabit Ethernet ISA 8-bit/4.77 MHz 5 EISA 6 PCIe Gen1x8 19 SATA 1.0 6 PCI 32-bit/33 MHz 6 Serial FPDP PCIe Gen2x8 PCle Gen1x1 7 7 PCI 32-bit/66 MHz PCIe Gen3x8 21 SATA 2.0 8 IDE (ATA PIO 0) 8 JESD204B 3G-SDI 9 ATA PIO 1 PCle Gen1x4 JESD204A 10 ATA PIO 2 Serial RapidIO Gen1.3 10 Gigabit Ethernet TATA PIO 3 PCle Gen2x4 22 PCle Gen2x1 USB 3.0 P ATA PIO 3 DisplayPort ISA 16-bit/8.33 MHz SATA 3.0 13 PCle Gen3x4 PCIe Gen3x1 HDMI 1.0 25 USB 3.1 DVI

FIG

5

The above shows well-known bus standards and their respective numbers of lanes versus line rates. The serial standards are capable of much higher line rates than the parallel standards, leading to higher throughput.

## Digital Instrument Categories

As with analog instrumentation, you can quickly narrow your options for digital instrumentation using a couple of key questions:

- What task do you need to accomplish? (digital interfacing, custom digital interfacing, or electrical and timing test)

- How fast is the link? (static and kilobit per second range, megabit per second, or gigabit per second)

|                                                   | STATIC, LOW SPEED                                                                                                | SYNCHRONOUS AND HIGH-SPEED<br>PARALLEL (100 MBITS/S RANGE) | HIGH-SPEED SERIAL (10<br>GBITS/S RANGE)                                              |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------|

| INTERFACE (STANDARD)                              | Low-Speed Standard Interface Card (I2C, C)<br>Synchronous Protocol Interface<br>(ARINC 429, CAN, GPIB, I2C, SPI) |                                                            | Interface Card<br>(10 Gigabit Ethernet,<br>Fibre Channel, PCI Express,<br>and so on) |

| INTERFACE (CUSTOM)                                | Digital I/O (GPIO)                                                                                               | Digital Waveform Generator/<br>Analyzer, Pattern Generator | FPGA-Based High-Speed Serial<br>Interface<br>Aurora, Serial Rapid I/O,<br>JESD204b   |

| ELECTRICAL TEST AND TIMING TEST (BASIC INTERFACE) | Pin Electronics Digital,<br>Per-Pin Parametric Measurement Unit (PPMU)                                           |                                                            | BERT, Oscilloscope                                                                   |

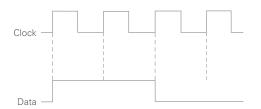

#### Hardware Versus Software Timing

You can implement digital communication schemes using two main methods: software timing and hardware timing. Softwaretimed applications do not use any type of clock for input or output. The software controls the I/O, and a programming language controls the timing through software. This programming language typically runs on an OS, which could take up to milliseconds to execute software calls. For software timing, you use the OS timer to determine the rate of timed actions. Generally, low-speed applications, such as monitoring and controlling alarms, motors, and enunciators, use software timing.

You can choose from two types of software-timed communication: deterministic control and nondeterministic control. Using a real-time OS, you can achieve precision of up to 1 µs; however, real-time OSs do not make communications faster, only more deterministic. Non-real-time systems, such as Microsoft Windows, are nondeterministic. In these systems, the time taken for software commands to execute in hardware is inconsistent and could take multiple milliseconds. Factors such as computer memory, processor speed, and other applications running on the OS could affect the execution time

With hardware-timed operations, you can take advantage of real-time, deterministic digital 6

Hardware-timed devices, in contrast, use the rising or falling edges of a clock for deterministic generation or acquisition. You can use this kind of timing to acquire or generate digital data at rates in the gigabit per second range with very high determinism, and you can reliably output data at predetermined locations.

Applications that use hardware timing include the following:

- Chip testing

- Protocol emulation and testing

- Digital video and audio testing

- Digital electronics testing

#### Clock Rate

An important consideration for hardware-timed digital applications is clock speed. The maximum speed that a device can achieve is difficult to compensate for if it is inadequate. You can achieve up to 200 MHz sampling rates for single-ended signals and up to 200 MHz for differential signals using NI high-speed digital I/O devices, thus enabling tests including protocol, digital audio and video, and digital electronic. For scenarios where a device might not meet the necessary clock rate requirements on a serial data stream, you can use serializers/deserializers (SERDES) to acquire higher frequency digital signals. However, depending on the type of SERDES you use, incorporating a SERDES might reduce the number of available lines..

## Form Factor

In addition to understanding the analog front end required to physically make the correct measurement, you need your instruments to be stable, repeatable, fast, and PC-connected—that's part of the job.

This brings you to a decision regarding the setting/environment:

- For the bench and lab—Accuracy, repeatability, low-level control, ease of setup, and ability to automate for repetitive tests

- For the manufacturing floor—Speed, throughput, accuracy, optimization through programming interface, and debugging

Clearly, there are similarities and differences in how you'd select instrumentation across the lab versus the manufacturing floor. You typically evaluate instrument form factors across a set of key success criteria for the end deployment. Below is a typical set of evaluation criteria you might see for a manufacturing environment.

#### Hardware Deployment Checklist

| FUNCTIONAL NEEDS                                             | TEST ENGINEERING NOTES |

|--------------------------------------------------------------|------------------------|

| Instrumentation, I/O needed?                                 |                        |

| Processing, compute needed?                                  |                        |

| Data throughput, storage?                                    |                        |

| Synchronization?                                             |                        |

| Future requirements?                                         |                        |

| Number of systems deployed over number of years?             |                        |

| Years of planned sustainment?                                |                        |

| Number of global sites replicating?                          |                        |

| Environmental stability of deployment scenarios?             |                        |

| How is the initial setup, configuration, and repair managed? |                        |

| Rack mounted?                                                |                        |

| Size, weight, and power?                                     |                        |

| Fixture and connectivity?                                    |                        |

## Selecting Bus Type

Today, USB, PCI Express, and Ethernet/LAN have gained attention as attractive communication options for instrument control. Some test and measurement vendors and industry

pundits have claimed that one of these buses, by itself, represents a solution for all instrumentation needs. In reality, it is most likely that multiple bus technologies will continue to coexist in future test and measurement systems because each bus has its own strengths.

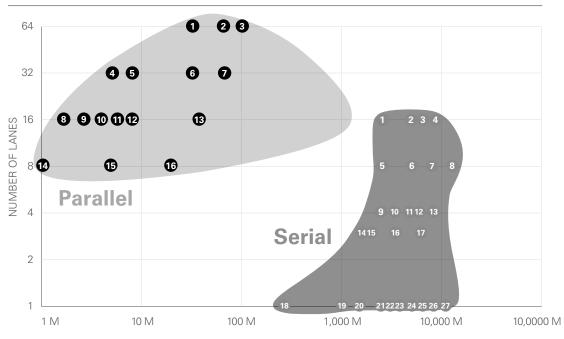

#### Bandwidth

When considering the technical merits of alternative buses, bandwidth and latency are two of the most important bus characteristics. Bandwidth measures the rate at which data is sent across the bus, typically in megabytes per second. A bus with high bandwidth can transmit more data in a given period than a bus with low bandwidth. Most users recognize the importance of bandwidth because it affects whether their data can be sent across the bus to or from a shared host processor as fast as it is acquired or generated and how much onboard memory their instruments will need. Bandwidth is important in applications such as complex waveform generation and acquisition as well as RF and communications applications. High-speed data transfer is particularly important for virtual and synthetic instrumentation architectures. The functionality and personality of a virtual or synthetic instrument is defined by software; in most cases, this means data must be moved to a host PC for processing and analysis. Figure 7 charts the bandwidth (and latency) of all the instrumentation buses examined in this guide.

### Latency

Latency measures the delay in data transmission across the bus. By analogy, if you were to compare an instrumentation bus to a highway, bandwidth would correspond to the number of lanes and the speed of travel, while latency would correspond to the delay introduced at the on and off ramps. A bus with low (meaning good) latency would introduce less delay between the time data was transmitted on one end and processed on the other. Latency, while less observable than

bandwidth, has a direct impact on applications where a quick succession of short, choppy commands is sent across the bus, such as in handshaking between a DMM and switch, and in instrument configuration.

#### **GPIB**

The IEEE 488 bus—commonly known as GPIB—is a proven bus designed specifically for instrument control applications. GPIB has been a robust, reliable communication bus for 30 years and is still the most popular choice for instrument control because of its low latency and acceptable bandwidth. It currently enjoys the widest industry adoption with a base of more than 10,000 instrument models with GPIB connectivity.

With a maximum bandwidth of about 1.8 Mbytes/s, it is best suited for communicating with and controlling stand-alone instruments. The more recent, high-speed revision, HS488, increased bandwidth up to 8 Mbytes/s. Transfers are message-based, often in the form of ASCII characters. Multiple GPIB instruments can be cabled together to a total distance of 20 m, and bandwidth is shared among all instruments on the bus. Despite relatively lower bandwidth, GPIB latency is significantly lower (better) than that of USB and especially Ethernet. GPIB instruments do not autodetect nor autoconfigure when connected to the system; though GPIB software is among the best available, and the rugged cable and connector are suitable for the most demanding physical environments. GPIB is ideal for automating existing equipment or for systems requiring highly specialized instruments.

Bandwidth versus latency for instrumentation buses

#### **USB**

USB has become popular in recent years for connecting computer peripherals. That popularity has spilled over into test and measurement with an increasing number of instrument vendors adding USB device controller capabilities to their instruments. Though most laptops, desktops, and servers may have several USB ports, those ports usually all connect to the same host controller, so the USB bandwidth is shared among all the ports.

Latency for USB falls into the better category (between Ethernet at the slow end and PCI and PCI Express at the fast end), and cable length is limited to 5 m. USB devices benefit from autodetection, which means that unlike other technologies, such as LAN or GPIB, USB devices are immediately recognized and configured by the PC when a user connects them. USB connectors are the least robust and least secure of the buses examined here. External cable ties may be needed to keep them in place.

USB devices are well suited for applications with portable measurements, laptop or desktop data logging, and in-vehicle data acquisition. The bus has become a popular communication choice for stand-alone instruments because of its ubiquity on PCs and especially its plug-and-play ease of use. The USB Test and Measurement Class (USBTMC) specification addresses the communication requirements of a broad range of test and measurement devices.

#### PCI

POI and POI Express achieve the best bandwidth and latency specifications among all the instrumentation buses examined here. POI bandwidth is 132 Mbytes/s, with that bandwidth shared across all devices on the bus. POI latency performance is outstanding—benchmarked at 700 ns, compared to 1 ms in Ethernet. POI uses register-based communication. Unlike the other buses mentioned here, POI does not cable to external instruments. Instead, it is an internal PO bus used for PO plug-in cards and in modular instrumentation systems, such as PXI, so distance measures do not directly apply. Nonetheless, the POI bus can be extended by up to 200 m by the use of NI fiber-optic MXI interfaces when connecting to a PXI system. Because the POI connection is internal to the computer, it is probably fair to characterize the connector robustness as being constrained by the stability and ruggedness of the PO in which it resides.

PXI modular instrumentation systems, which are built around PCI signaling, enhance this connectivity with a high-performance backplane connector and multiple screw terminals to keep

connections in place. Once booted with PCI or PXI modules in place, Windows automatically detects and installs the drivers for modules. In general, PCI instruments can achieve lower costs because they rely on the power source, processor, display, and memory of the PC that hosts them rather than incorporating that hardware in the instrument itself.

### **PCI Express**

PCI Express is similar to PCI. It is the latest evolution of the PCI standard. Therefore, much of the prior evaluation of PCI applies to PCI Express as well.

The main difference between PCI and PCI Express performance is that PCI Express is a higher bandwidth bus and gives dedicated bandwidth to each device. Of all the buses covered in this guide, only PCI Express offers dedicated bandwidth to each peripheral on the bus. GPIB, USB, and LAN divide bandwidth across the connected peripherals. Data is transmitted across point-to-point connections called lanes at 250 Mbytes/s per direction for Gen 1 link. Each PCI Express link can be composed of multiple lanes, so the bandwidth of the PCI Express bus depends on how it is implemented in the slot and device. A x1 (by 1) link provides 250 Mbytes/s, a x4 link provides 1 Gbyte/s, and a x16 link provides 4 Gbytes/s dedicated bandwidth. PCI Express achieves software backward compatibility, meaning that users moving to the PCI Express standard can preserve their software investments in PCI. PCI Express is also extensible by external cabling.

High-speed, internal PC buses were designed for rapid communication. Consequently, PCI Express is an ideal bus choice for high-performance, data-intensive systems where large bandwidth is required and for integrating and synchronizing several types of instruments.

## Ethernet/LAN/LXI

Ethernet has long been an instrument control option. It is a mature bus technology and has been widely used in many application areas outside test and measurement. 100BASE-T Ethernet has a theoretical max bandwidth of 12.5 Mbytes/s. Gigabit Ethernet, or 1000BASE-T, increases the max bandwidth to 125 Mbytes/s. In all cases, Ethernet bandwidth is shared across the network. At 125 Mbytes/s Gigabit Ethernet is theoretically faster than Hi-Speed USB, but this performance quickly declines when multiple instruments and other devices are sharing network bandwidth. Communication along the bus is message-based, with communication packets adding significant overhead to data transmission. For this reason, Ethernet has the worst latency of the bus technologies featured in this guide.

Nonetheless, Ethernet remains a powerful option for creating a network of distributed systems. It can operate at distances up to 85 m to 100 m without repeaters and has no distance limits with repeaters. No other bus has this range of separation from the controlling PC or platform. As with GPIB, autoconfiguration is unavailable on Ethernet/LAN. You must manually assign an IP address and subnet configuration to your instrument. Like USB and PCI, Ethernet/LAN connections are ubiquitous in modern PCs. This makes Ethernet ideal for distributed systems and remote monitoring. It is often used in conjunction with other bus and platform technologies to connect measurement system nodes. These local nodes may themselves be composed of measurement systems relying on GPIB, USB, and PCI. Physical Ethernet connections are more robust than USB connections, but less so than GPIB or PXI.

LAN eXtensions for Instrumentation (LXI) is an emerging LAN-based standard. The LXI standard defines a specification for stand-alone instruments with Ethernet connectivity that adds triggering and synchronization features.

Despite the conceptual convenience of designating a single bus or communication standard as the ultimate or ideal technology, history shows that several alternative standards are likely to continue to coexist, because each bus technology has unique strengths and weaknesses. Table 4 compiles the performance criteria from the previous section. It should be clear that no single bus is superior across all measures of performance.

You can exploit the strengths of several buses and platforms by creating hybrid test and measurement systems that combine

components from modular instrumentation platforms, such as PXI and stand-alone instruments, that connect across GPIB, USB, and Ethernet/LAN. One key to creating and maintaining a hybrid system is implementing a system architecture that transparently recognizes multiple bus technologies and takes advantage of an open, multivendor computing platform, such as PXI, to achieve I/O connectivity.

The other key to successfully developing a hybrid system is ensuring that the software you choose at the driver, application, and test system management levels is modular. Though some vendors may offer vertical software solutions for specific instruments, the most useful system architecture is one that breaks up the software functions into interchangeable modular layers so that your system is neither tied to a particular piece of hardware nor to a particular vendor. This layered approach provides the best code reuse, modularity, and longevity. For example, Virtual Instrument Software Architecture (VISA) is a vendor-neutral software standard for configuring, programming, and troubleshooting instrumentation systems comprising GPIB, serial (RS232/485), Ethernet, USB, and/or IEEE 1394 interfaces. It is a useful tool because the API for programming VISA functions is similar for a variety of communication interfaces.

With hybrid systems, you can combine the strengths of many types of instruments, including legacy equipment and specialized devices. Despite the appeal of finding a one-size-fits-all solution for instrumentation, reality requires that you fit the instruments and associated bus technologies to your specific application needs.

#### **Bus Performance Comparison**

|                              | BANDWIDTH (MBYTES/S)         | LATENCY (µS)                    | RANGE (M) (WITHOUT EXTENDERS) | SETUP AND INSTALLATION | CONNECTOR<br>RUGGEDNESS  |

|------------------------------|------------------------------|---------------------------------|-------------------------------|------------------------|--------------------------|

| GPIB                         | 1.8 (488.1)<br>8 (HS488)     | 30                              | 20                            | Good                   | Best                     |

| USB                          | 60 (USB 2.0)                 | Analog Output                   | 5                             | Best                   | Good                     |

| PCI (PXI)                    | 132                          | 0.7                             | Internal PC Bus               | Better                 | Better Best<br>(for PXI) |

| PCI EXPRESS<br>(PXI EXPRESS) | 250 (x1)<br>4,000 (x16)      | 0.7 (x1)<br>0.7 (x4)            | Internal PC Bus               | Better                 | Better Best<br>(for PXI) |

| ETHERNET/LAN/LXI             | 12.5 (Fast)<br>125 (Gigabit) | 1,000 (Fast)<br>1,000 (Gigabit) | 100 m                         | Good                   | Good                     |

## Timing and Synchronization

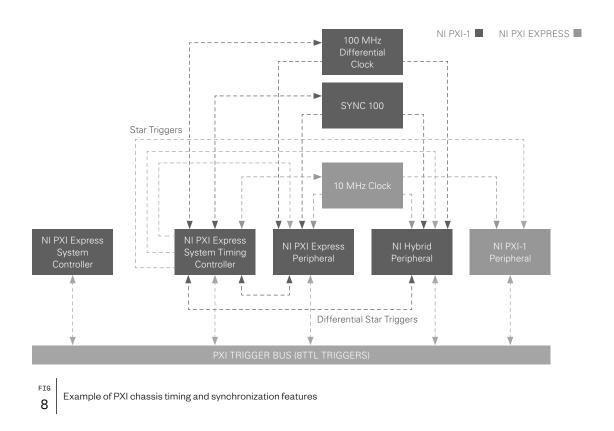

You can find a good example of integrated timing and synchronization between instruments in the PXI platform, a modular standard for test and measurement. PXI Express maintains the 10 MHz backplane clock as well as the single-ended PXI trigger bus and length-matched PXI star trigger signal that the original PXI specification provides.

PXI Express also adds a 100 MHz differential clock and differential star triggers to the backplane to offer increased noise immunity and industry-leading synchronization accuracy (250 ps and 500 ps of module-to-module skew, respectively). NI timing and synchronization modules are designed to take advantage of the advanced timing and triggering technology featured in its PXI and PXI Express chassis.

# **Next Steps**

Learn more about the basics of using test and measurement instrumentation by reading the white paper series, Instrument Fundamentals. This series covers topics ranging from analog sampling theory to grounding considerations for improved measurements.

# Automated Test System Power Infrastructure

27 INTRODUCTION

28 INTRODUCING POWER TO THE SYSTEM

29 GEOGRAPHIC LOCATION CONSIDERATIONS

31 ELECTROMAGNETIC INTERFERENCE OR LINE FILTERS

32 POWER BUDGET

35 POWER DISTRIBUTION UNIT

UNINTERRUPTABLE POWER SUPPLIES

38 POWER STATES

40 GROUNDING

41 BEST PRACTICES FOR COMPONENTS

## Introduction

Powering an automated test system, or automated test equipment (ATE), is different from powering the PC and lamp on your desk. Test systems are composed of many heterogeneous internal components, some of which require large amounts of current and power, and these systems are often deployed globally into facilities with differing power sources and quality. Many test system components are sourced from multiple vendors and must be integrated by the test engineers, which complicates matters even more. Choosing the right components and making the right design decisions is much simpler when you follow best practices in power layout and equipment selection.

A power layout ensures all components operate properly by avoiding bottlenecks where a component may need more power than the power distribution can provide. This is especially important for components that could compromise operation of the whole system if starved of power. This guide covers test system power planning by listing the steps and considerations for creating a power layout.

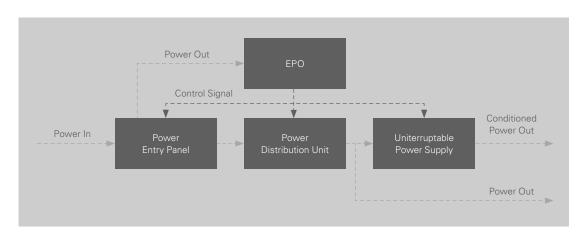

A power layout includes all equipment in the test system and maps the flow of power from the source to the test system to the end consumer.

# Introducing Power to the System

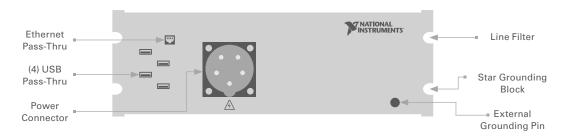

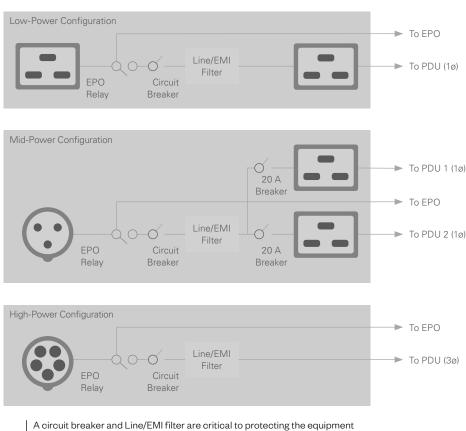

A best practice for introducing power to the ATE system is to use a power entry panel, or power inlet panel. This allows you to isolate the internal power cabling from the point at which the main voltage is applied. With a power entry panel, you can outfit your test system with the proper power connector rated for the voltage and current that will be powering the system. NI power entry panels use a number of connector types and power ratings for a variety of power requirements and geographic coverage. Figure 1 shows examples of power panel connectors. A good power panel should also have built-in circuit protection, including a circuit breaker and fuses, which protects the system from power surges or incorrect supply power. A great power panel has a built-in electromagnetic interference (EMI) filter, surge suppression, and other connectivity to pass signals into the system.

Low-Power Configuration

- IEC 60320 (C20)

- 1ø (16 A) 100-240 V

Medium-Power Configuration

- IEC 60309

- 1ø (32 A) 100-240 V

**High-Power Configuration**

- IEC 60309

- 3ø (16 A) 380-480 V (Red:3P+N+E)

A power entry panel provides connectivity for incoming power to the system. Power entry panels can have one of a number of standard power connector types and good power panels have additional features like filtering or kill-switch relays.

## **Geographic Location Considerations**

The geographic location of the tester or test facility is a critical detail in choosing the power panel for your test system. Additionally, when planning a new test system, consider the power standards and grid infrastructure, safety requirements, and ease of deployment, which are all factors that location can affect.

#### Power Grid Standards

The line power available from the public grid differs from country to country. Countries around the world have standardized on different RMS voltage levels, AC power frequency, connectors, and current ranges in their power grids.

There are several types of power configurations in public grids:

- Single-phase power uses a single active line that conducts an AC power and a neutral line. Common voltage levels of these lines vary from 100 V to 240 V. For instance, line power in Japan is 100 V, while power is delivered between 220 V and 240 V. The United States and Canada transmit power in public grids at 110 V to 120 V.

- Dual- or split-phase power is composed of two active lines that supply power at a given positive and negative offset voltage and one neutral wire. A common implementation of dual-phase power in the United States is 120 V with a 180 degree offset between active lines. Having two wires that are transmitting power with voltage levels of 120 V and -120 V allows you to have two single-phase sources of power with 120 V of potential by using each active line and the neutral line or one single-phase source with 240 V of potential by using the two active lines.

- Three-phase power is made up of three active lines that are 120 degrees offset from one another and one neutral wire. Most US buildings use 208 Y/120 V power, which has three lines that conduct 120 V power and a constant power circuit output of 208 V. Many industrial buildings use 480 Y/277 V, which provides 480 V for larger machinery.

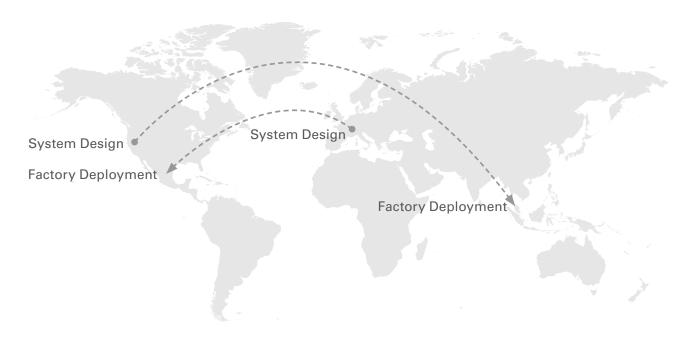

### Global Deployment

Test systems are often designed and deployed in separate or multiple locations. Having a single system deployed in multiple locations introduces new sets of system requirements. Deploying a system to Malaysia is different from deploying a system to a factory in the same country or even the same building. For example, you may build a test system for automotive engine control units at an R&D facility in Detroit but deploy it to factories in Mexico. Consider the power grid standards and quality when designing the system and confirm that all safety and regulatory certifications needed to deploy in Mexico are met before you ship the system. Here is a checklist of items to think through when designing a test system that will be globally deployed:

- Power grid voltage standard and configuration

- Power grid quality and reliability

- Materials compliance like RoHS

- Energy compliance like CE, PSE, or KC

- Trade compliance and import/export regulations

If you plan to deploy the test system to countries or regions outside the test system's country of origin, know the available power in the location(s) that the test system will be deployed and if you need to convert that power to operate the equipment in your test system. In the example above, the test systems were going to Malaysia and Mexico. Luckily, the power grids in both the United States and Mexico provide power at 110 V to 120 V and 60 Hz. This gets a bit more complex for a test station designed in Germany and deployed to Mexico where mains voltages are different.

Power converters and uninterruptable power supplies (UPSs) can help you to condition standard power to meet the needs of the system. For example, a test system that includes equipment that accepts only 120 V may need to include a power converter to turn 230 V single-phase power into a single-phase 120 V supply for the instrumentation. Better yet, evaluate and select equipment that has global input voltage to avoid the hassle altogether.

#### Certification

Many countries have specific required electrical safety standards like CE in Europe, PSE in Japan, or KO in Korea. Compliance testing for electrical test equipment usually includes emissions level and frequency, touch safety, and surge protection. The most important reason to get these markings is to be able to deploy systems to other countries or certify a factory for operation. Do the necessary research to know the required certifications in each country in which the test system will operate. Ignoring the certifications could make it problematic to service test systems in the future. Individual components cannot be imported unless they have these marks, so it is difficult to replace or repair parts that lack proper certification.

FIG

Designing and deploying test systems in multiple countries requires you to be flexible in designing your system. Consider power standards and certifications whenever you are developing a test system that could be used in multiple locations.

# **Electromagnetic Interference or Line Filters**

Power grids carry high-energy signals that emit electromagnetic noise. Most noise from power lines is relatively consistent and you can plan for it in advance. No grid is perfect, however, so there will most likely be some nonstandard noise in the power signal. Nonstandard noise can affect the measurements taken by instrumentation in the system or cause the system to violate certification requirements. EMI and line filters are the most common ways to protect the test system from unexpected noise sources emanating from power transmission lines. A line filter is specified for a given voltage level, a maximum current level that should not be exceeded, and an operating range for frequencies it filters from the signal. For example, a line filter may be designed for 250 V, 10 A, and operate from 150 kHz to 1 MHz. Be sure to choose the right line filter for the power and unwanted noise frequencies in your test system. NI power entry panels include EMI/line filters to protect sensitive measurement equipment.

A circuit breaker and Line/Emittiter are critical to protecting the equipment in your test system and ensuring proper and accurate performance of your distribution. Example power entry panels are shown for low-power, mid-power, and high-power configurations.

# Power Budget

A power budget is a critical part of planning resources and components for a test system. A given piece of equipment must have access to the proper amount of current at the correct voltage level. Budgeting must be performed for the entire system and at each point that power is distributed within the system. After determining the amount of power required, you can apply a few standard rules to the calculated values to right-size the power allocations in the test system.

## System Power Budget

A system power budget begins with finding the maximum power requirements of all equipment included in the test system. The sum total should contain the expected power draw of all components in the test system, including voltage, current, and watts of power. In many cases, the most important part of power budgeting is the current. Only a certain amount of current can flow through a given transmission line in the system, so current often has to be carefully distributed throughout the system using a power distribution unit (PDU).

The power draw of a given device is generally published in the user manual and sometimes includes a number of power requirements at different conditions. Occasionally, devices have specified typical power consumption and a maximum or worst-case power consumption specification. As a best practice, use the maximum power requirement as a conservative safety measure, and then subtract a given percentage, usually 30 to 40 percent, for a more realistic measure. Figure 5 shows the maximum power requirement of a stand-alone instrument that would be integrated into a test system.

The VirtualBench all-in-one instrument specifies maximum power required at times of high-energy usage as opposed to typical or average power.

| CAUTION: THE PROTECTION PROVIDED BY THE VIRTUALBENCH HARDWARE CAN BE IMPAIRED IF IT IS USED IN A MANNER NOT DESCRIBED IN THE NI VB-8034 SAFETY, ENVIRONMENTAL, AND REGULATORY INFORMATION DOCUMENT. |                                                                                                                                                                                                                             |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Voltage Input Range                                                                                                                                                                                 | 100 VAC to 240 VAC, 50/60 Hz                                                                                                                                                                                                |  |

| Power Consumption                                                                                                                                                                                   | 150 W maximum                                                                                                                                                                                                               |  |

| Power Input Connector                                                                                                                                                                               | IEC C13 power connector                                                                                                                                                                                                     |  |

| Power Disconnect                                                                                                                                                                                    | The AC power cable provides main power disconnect. Do not position the equipment so that it is difficult to disconnect the power cable. Depressing the front panel power button does not inhibit the internal power supply. |  |

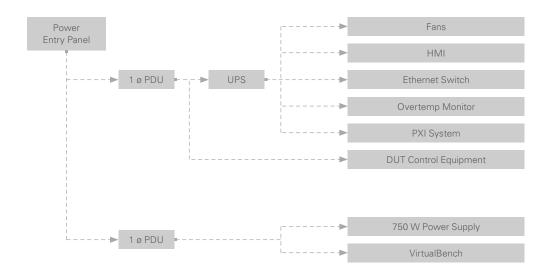

As a quick and simple example, consider the test system in Table 1. First collect the maximum power consumption of each piece of equipment in the test system. Make sure to account for subsystems and bottlenecks. PDUs have a maximum current limit—in this case 16 A—so plan accordingly. The next step is to correct these values for typical power required as opposed to maximum. This means taking about 60 to 70 percent of that value. In this case, that gives you approximately 1,920 W for this test system using 70 percent as a conservative measure. It may also be a good idea to add about 20 percent of this full value as a means of expanding or adding new functionality to the system in the future without having to add more power to the system.

| EQUIPMENT          | MAXIMUM POWER CONSUMPTION | AVERAGE POWER UTILIZATION | CURRENT AT 110 V |

|--------------------|---------------------------|---------------------------|------------------|

| PDU 1              |                           |                           |                  |

| Fans               | 50 W                      | 35 W                      | .03 A            |

| HMI                | 100 W                     | 70 W                      | .06 A            |

| Ehternet Switch    | 25 W                      | 17.5 W                    | .02 A            |

| Overtemp Monitor   | 10 W                      | 7 W                       | .01 A            |

| PXI System         | 526.9 W                   | 369 W                     | 3.4 A            |

| DUT Control Pumps  | 1,000 W                   | 700 W                     | 6.4 A            |

| PDU 1 Total        |                           | 1,198.5 W                 | 11.0 A           |

|                    |                           |                           |                  |

| PDU 2              |                           |                           |                  |

| VirtualBench       | 150 W                     | 105 W                     | 1.0 A            |

| 750 W Power Supply | 1,100 W                   | 770 W                     | 7.0 A            |

| PDU 2 Total        |                           | 875 W                     | 8.0 A            |

|                    |                           |                           |                  |

| System Total       |                           | 2,073.5 W                 | 19.0 A           |

Start calculating a power budget by collecting the maximum power consumption of all system components, applying an average power utilization factor, and adding them together. Remember to account for bottlenecks and subsystems.

Three easy best practices can significantly simplify power budgeting:

- Base your system power requirements on about 60 to 70 percent of the maximum required power of each component.

- 02 Add about 20 percent to the final power calculation from rule one as a safety buffer to account for high-activity periods and any necessary future expansion of the test system.

- 03 Remember that some items connect through PDUs and UPSs, so there are power subsystems within the larger system.

## Subsystem Power Budget

A step not included in solving for the power budget above is how to account for subsystems within the large test rack. A subsystem can be any subset of the equipment in the larger test system that all share a common power source. This may be a number of instruments using a single bank of a PDU or a modular instrumentation system like PXI.

A benefit of modular instrumentation is that it can simplify power management. If all the instruments included in the PXI chassis were separate in the test system, you would have to account for each of them individually. PXI chassis provide high-quality and safe power to all instruments in the chassis and come in several power and instrumentation slot options.

When adding a PXI system to your power budget, you can take one of two options:

- Use the maximum power consumption of a full PXI system as specified by the PXI chassis. For example, the maximum power consumption of a PXIe-1085 PXI Chassis is 791 W, which would translate to a budgeted power consumption of 554 W after applying an average utilization factor of 70 percent.

- Add the maximum power consumptions of all modules in the PXI system to get a very accurate power budget number. See Figure 6 for an example of performing a detailed PXI system power budget.

Additionally, a modular instrumentation system is significantly more efficient than a traditional set of instruments because it removes the shared components like monitors and cooling that would have to be powered within a test system.

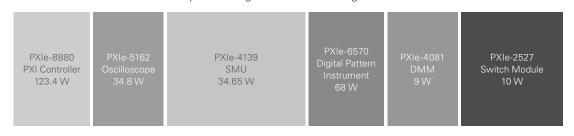

As an example of an accurate power budget for a PXI system, consider a PXIe-1085 PXI Chassis with 24 GB/s system throughput that includes a PXIe-8880 PXI Controller, six PXIe-4139 precision system source measure units (SMUs), two PXIe-5162 PXI Oscilloscopes, a PXIe-6570 digital pattern instrument, two PXIe-4081 7 ½-digit digital multimeters (DMMs), and four PXIe-2527 multiplexer switch modules. See a representation of how the PXI system power budget is calculated in Figure 6.

Maximum Available Power in PXI Chassis is 791 W Maximum Total Power Consumption of the System is 526.9 W Power Consumption Taking into Account Average Utilization is 369 W

FTG The total power consumption of a PXI Chassis is the sum of all modules in the chassis. You can see above a full chassis of 6 instrumentation that will, in the worst-case scenario, consume 526.9 W.

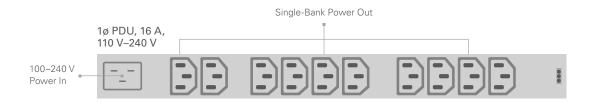

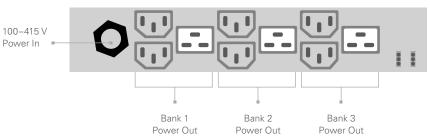

## **Power Distribution Unit**

A PDU's main purpose is to take an input power signal and distribute it to a number of outputs that power components of the system. These internal power outlets from the PDU have a rated voltage and current and are often available for both alternating and direct current.

The best PDU options have a number of features:

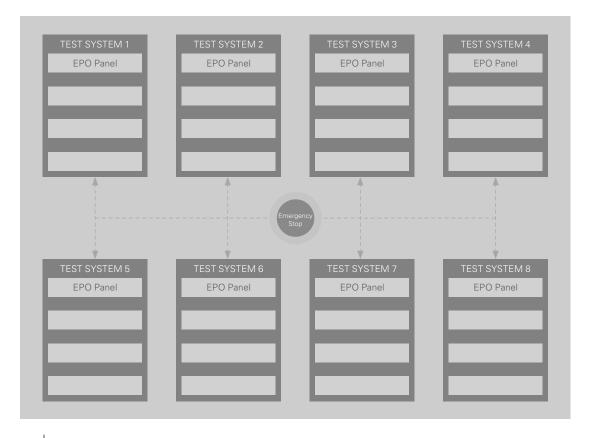

- Remote on/off gives operators the ability to make changes in the power state with the power mechanism and EPO. In this way, the operator has full control of the system state from an easily accessible location. Operators also can disable the power in the system from the local and global EPO mechanism.

- Built-in circuit protection like fuses can protect valuable and fragile equipment from unexpected power events, which could save tens, or even hundreds of thousands of dollars.

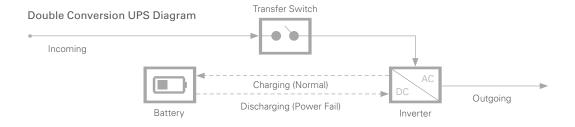

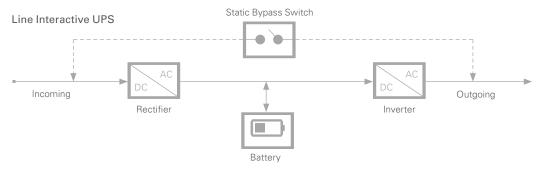

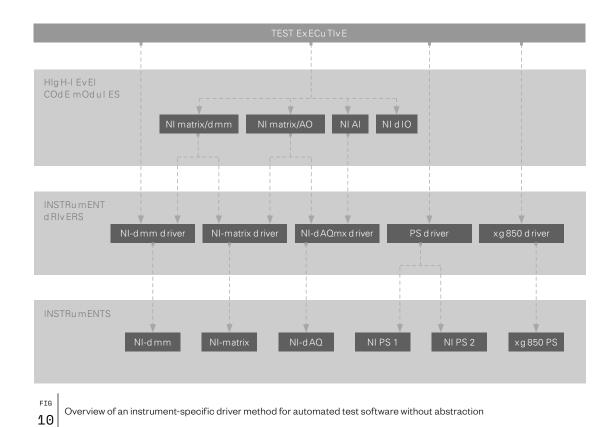

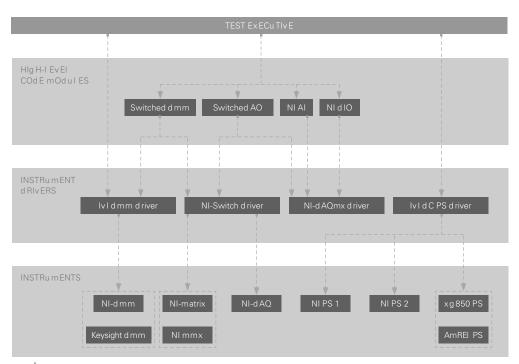

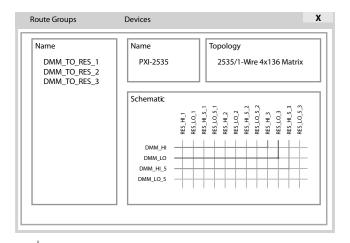

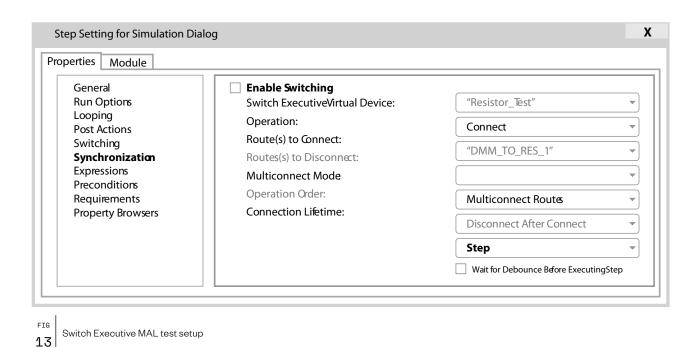

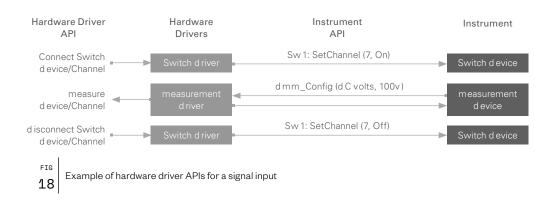

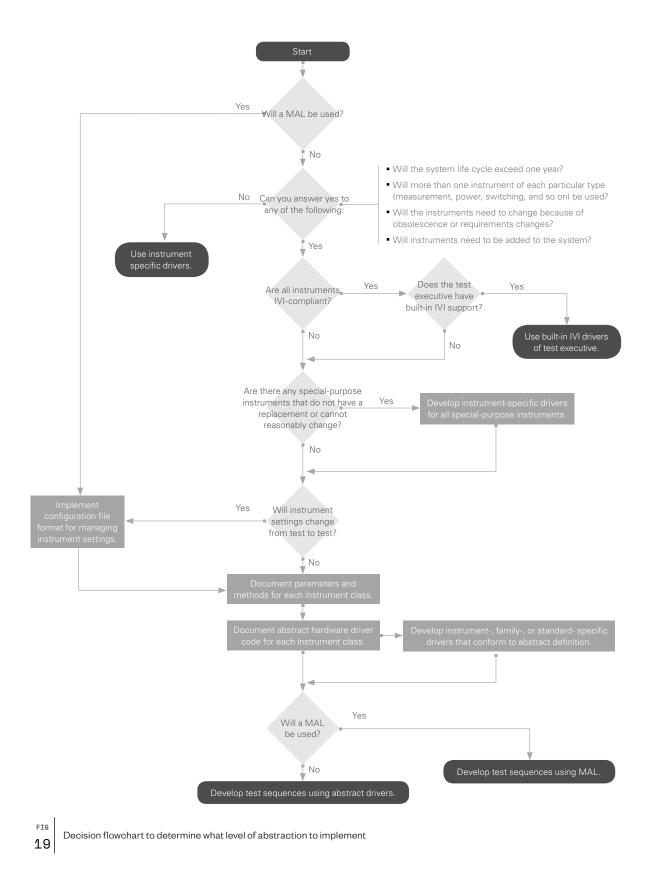

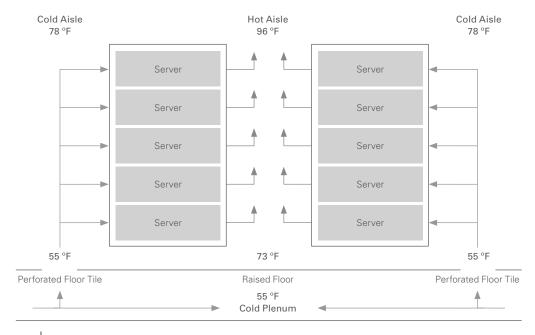

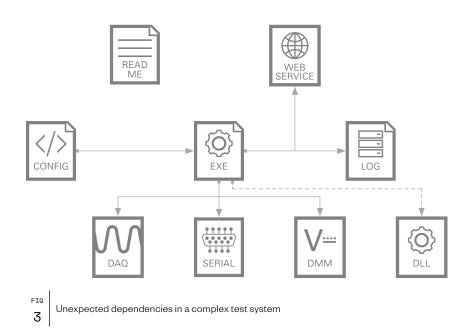

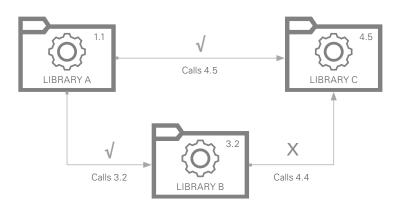

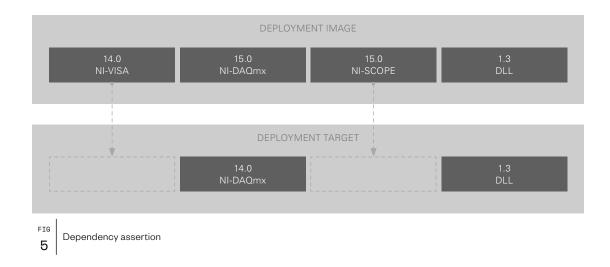

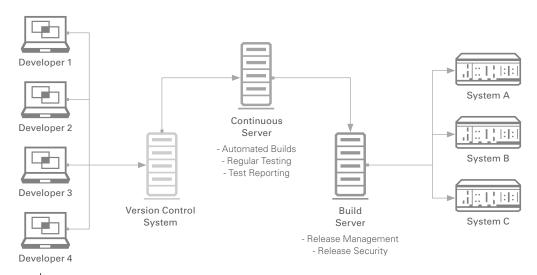

- Bank sequencing can ensure that specific equipment powers on first before other banks power on. For instance, a PXI chassis that is connected to an external controller, or extended from another master PXI chassis, needs to start before the host controller. In this case, the PDU should enable a bank of outlets that include the slave PXI chassis before starting the bank that includes the master PXI chassis.